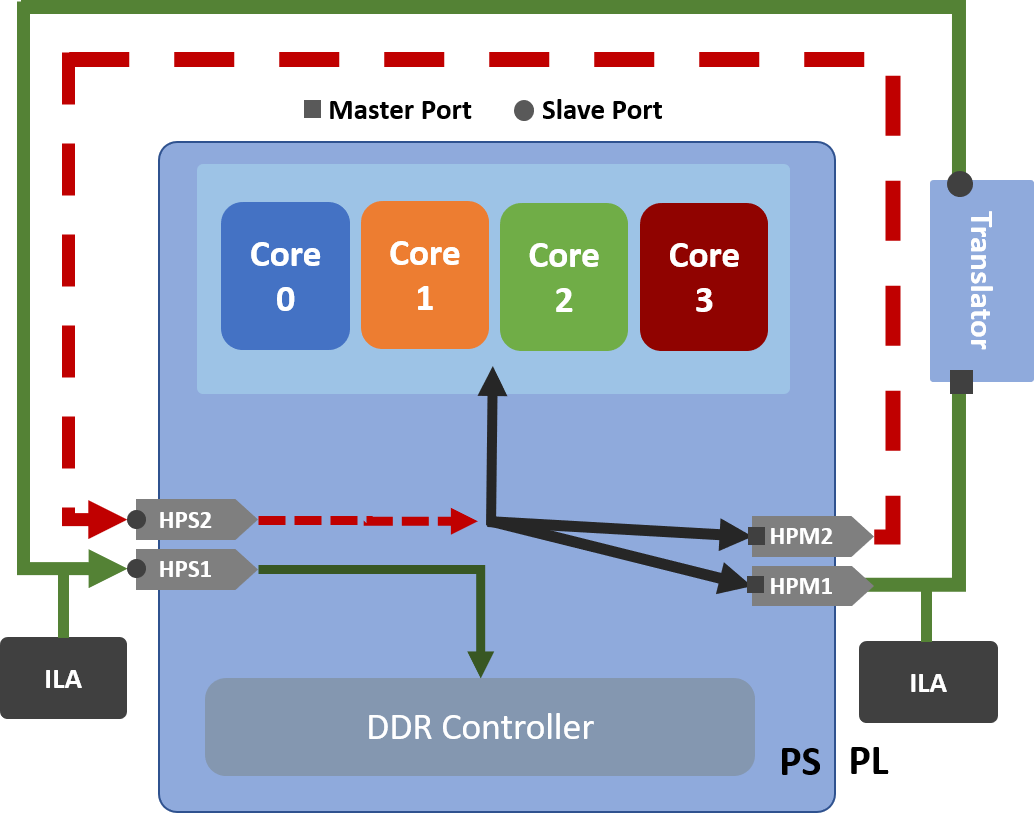

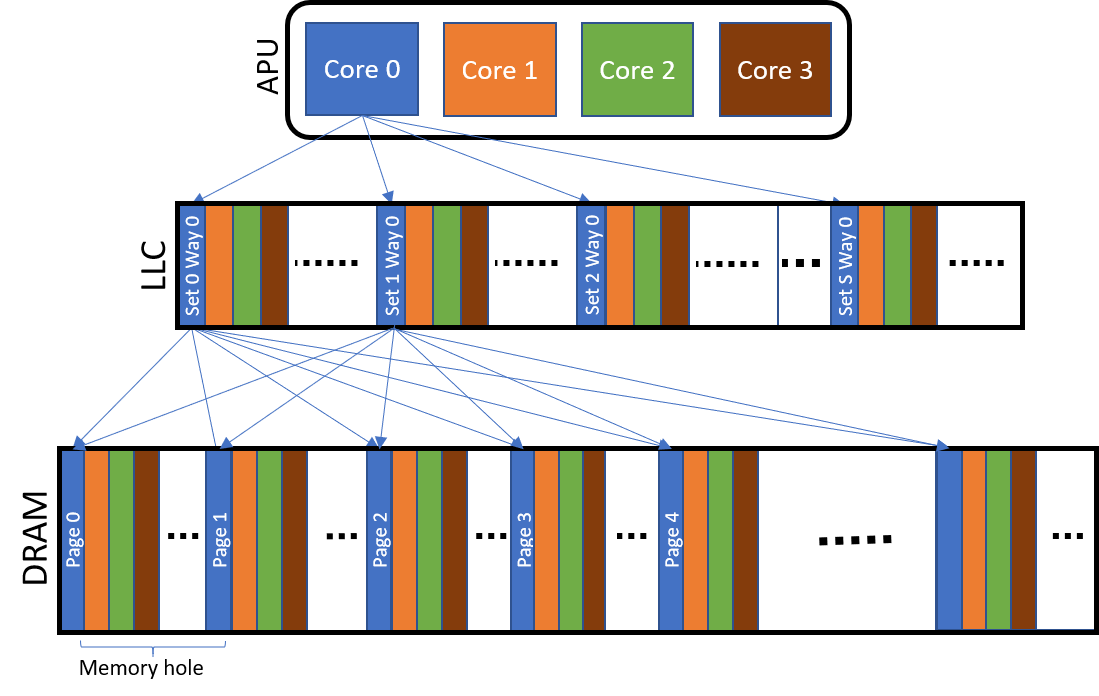

Strong from the observation that unpredictability arises from a lack of fine-grained control over the behavior of shared hardware components, we outline a promising new resource management approach. We demonstrate that it is possible to introduce Programmable Logic In-the-Middle (PLIM) between a traditional multi-core processor and main memory. This provides the unique capability of manipulating individual memory transactions.

Congratulations Shahin Roozkhosh and Renato Mancuso from Boston University for winning Best Paper @RTAS2020 for The Potential of Programmable Logic in the Middle: Cache Bleaching: https://t.co/DB41KszTXn

— Gernot Heiser (@GernotHeiser) April 21, 2020

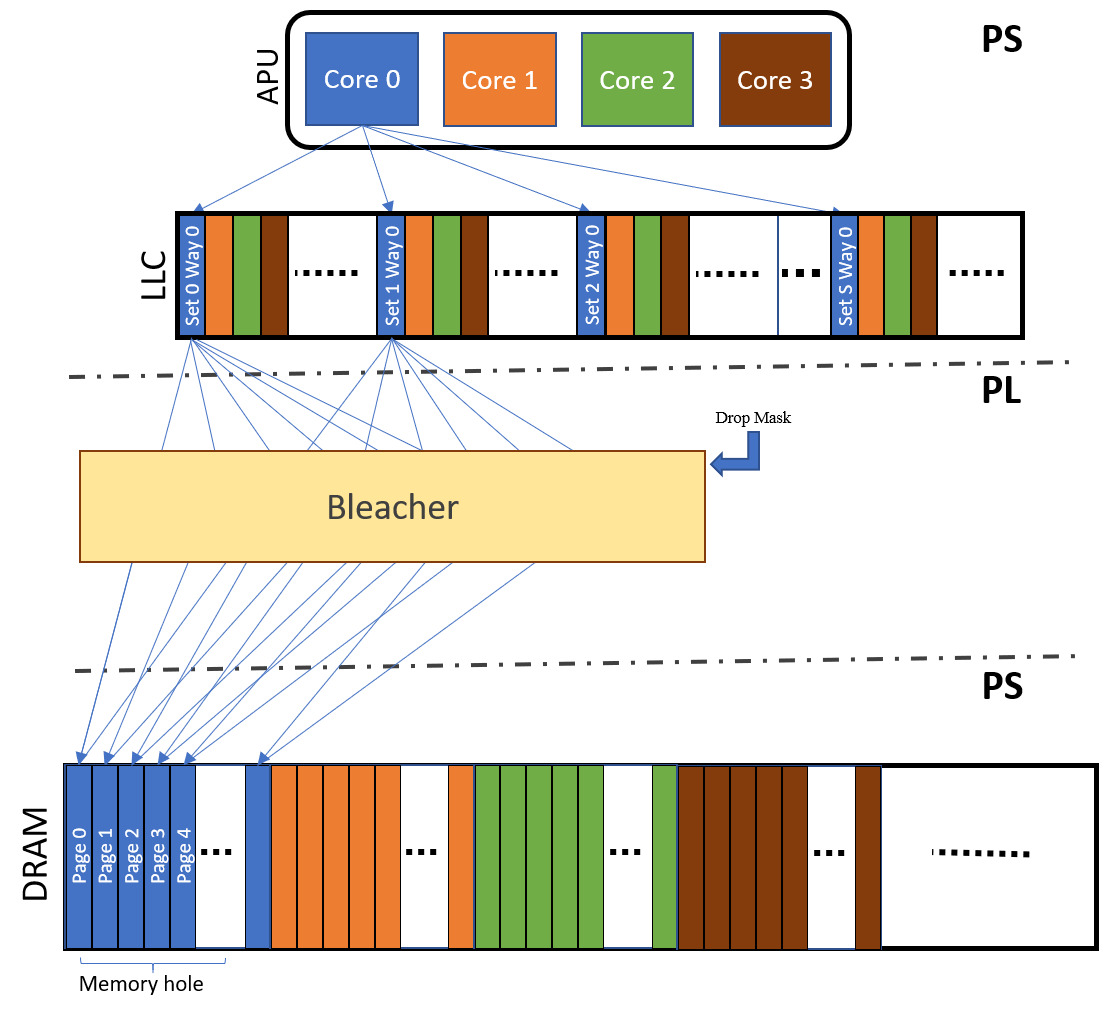

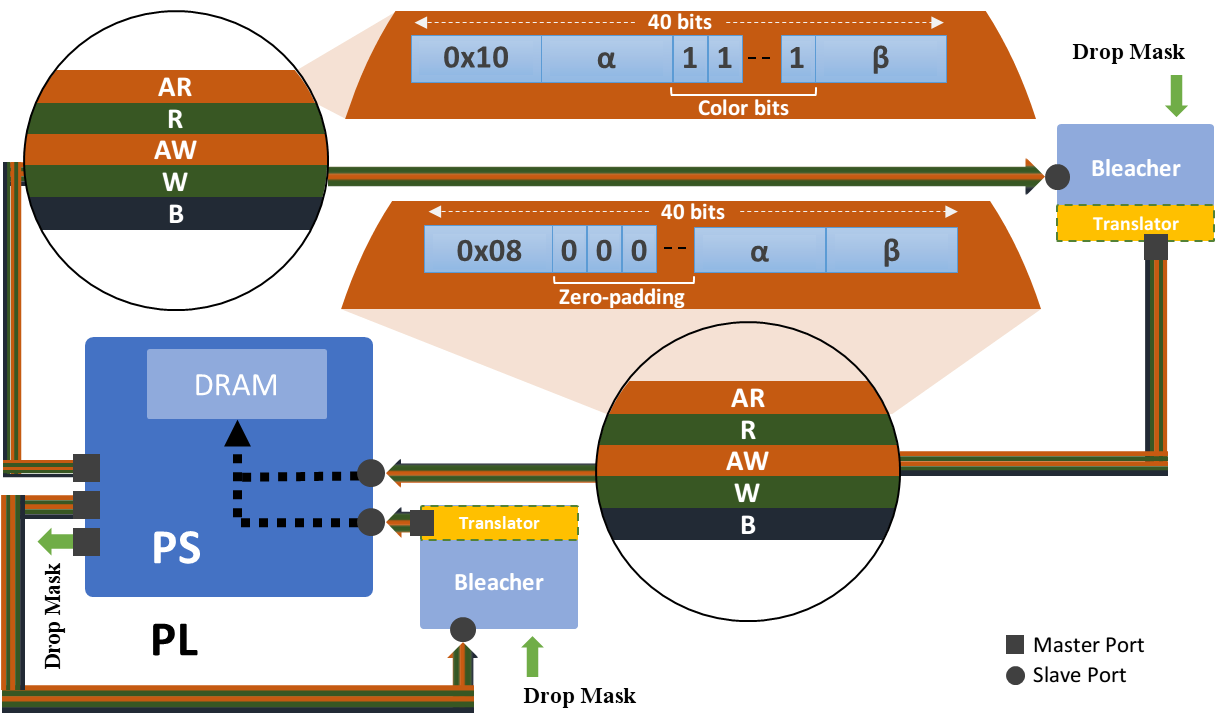

We proposed, implemented, and evaluated a first technique, Cache Bleaching, that leverages PLIM to solve long-standing shortcomings of page-coloring-based cache partitioning.

We demonstrate that under PLIM it is possible to obtain an unprecedented level of inspection on the behavior of last-level caches (LLC) and main memory

Fragmented DRAM

With the Bleacher (right), colored addresses are de-colored hence, previously scattered pages (left) become contiguous in DRAM

Contiguous DRAM with PLIM